# WTL 1164/WTL 1165 64-BIT IEEE FLOATING POINT MULTIPLIER/DIVIDER AND ALU

#### PRELIMINARY DATA

#### **Features**

A COMPLETE FLOATING POINT ARITHMETIC SOLUTION FOR HIGH-SPEED PROCESSORS AND COPROCESSORS

FULL 32-BIT AND 64-BIT FLOATING POINT FORMAT AND OPERATIONS, CONFORMING TO THE IEEE STANDARD FOR FLOATING POINT ARITHMETIC

INTERFACE CHIPS TO POPULAR 32-BIT MICROPROCESSORS AVAILABLE

#### **FULL FUNCTION**

Addition

Subtraction

Multiplication

Division

Conversion to and from 32-bit two's complement integers

Absolute value

Compare

INTERFACES DIRECTLY TO 32-BIT BUSES

SINGLE PHASE, EDGE-TRIGGERED CLOCKED INTERFACE WITH FULLY REGISTERED INPUTS AND OUTPUTS

#### HIGH SPEED

2.38 MFlops (420 ns) 32-bit add/subtract/convert and compare

1.85 MFlops (540 ns) 64-bit add/subtract/convert and compare

2.38 MFlops (420 ns) 32-bit multiply

1.67 MFlops (600 ns) 64-bit multiply

0.52 MFlops (1.92 µs) 32-bit divide

0.26 MFlops (3.78 µs) 64-bit divide

Up to 3.33 MFlops (300 ns) for pipelined operations

Up to 3.33 MFlops (300 ns) for chained operations

32-bit data input or 32-bit data output operation every 60 ns

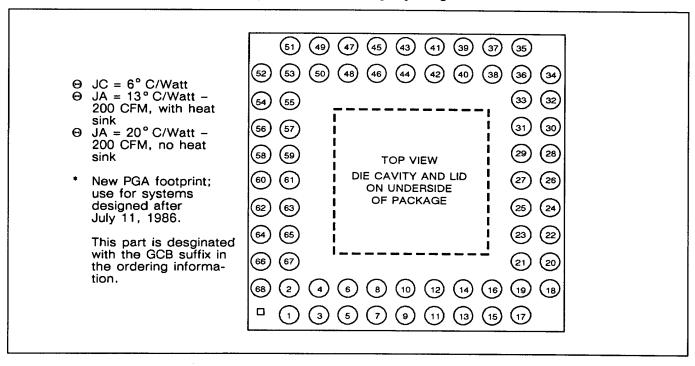

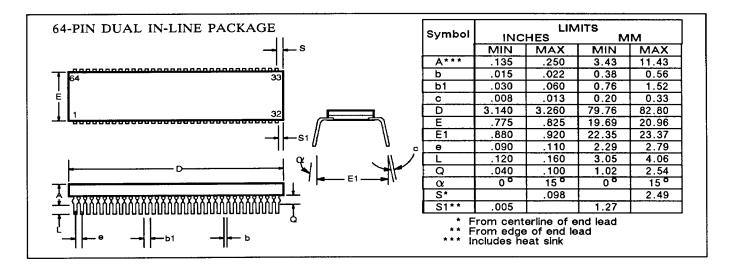

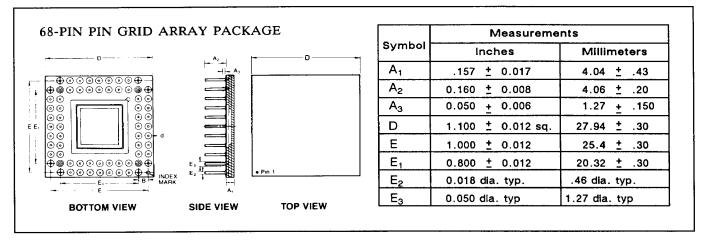

STANDARD 64-PIN DIP AND 68-PIN PGA PACKAGES

## Description

The WTL 1164 floating point multiplier and the WTL 1165 floating point arithmetic logic (ALU) unit are designed to provide high-speed 32-bit and 64-bit floating point processing capability. By virtue of their high performance, simple interface and ease of control, the WTL 1164/1165 are ideal choices for high performance floating point coprocessors. In fact, the bus interface and control of the WTL 1164/1165 are so simple that all of the logic required to implement a memory-mapped coprocessor to industry standard microprocessors can be put on a single chip. A short application note explaining how a single chip, the WTL 1163, can interface the WTL 1164/1165 to Intel's 80386 is attached.

This two-chip set can handle both single (32-bit) and double (64-bit) precision IEEE formats and operations, as well as full 32-bit two's complement integers. The NMOS VLSI design allows all of the functional elements to be combined on two chips while very flexible input/output path and control signals permit the WTL 1164/1165 to work in a broad range of bus systems and a wide variety of applications.

The data format and floating point operations conform to the requirements of the IEEE Standard for Binary

Floating Point, including all rounding modes, infinity, NaN, denormalized and zero operand representations, and the treatment of exceptions, such as overflow, underflow, divide-by-zero, invalid and inexact operations. This assures complete software portability between systems designed using these parts and other general purpose computer systems which may be used to prototype algorithms and applications software. A "FAST" mode of operation, which removes the time penalty of underflow exception handling by substitution of zero for denormalized numbers while retaining all the other features, is included.

The WTL 1164/1165 use dedicated circuit arrays to perform the required functions, providing significantly faster processing than designs which must rely solely on sequential, clocked logic. The array flowthrough time for the WTL 1164 is under 240 ns for a single precision (32-bit) multiply and under 360 ns for a double precision (64-bit) multiply. For the WTL 1165, the array flowthrough time is under 240 ns for both single and double precision functions. These figures include the time for performing the arithmetic function as well as denormalization, renormalization and exponent adjustments.

## Description, continued

Although division operations do not occur as frequently as addition, subtraction or multiplication operations, systems performing floating point arithmetic in close accordance with the IEEE standard require a floating point division operation which meets the requirements for accuracy specified by the standard. The division operation provided on the WTL 1165 floating point ALU fully conforms with the IEEE standard.

Data input and output transfers may occur at a rate of one transfer per clock cycle, permitting the devices to be used in variety of bus configurations without degrading performance. Two double precision inputs can be loaded through the 32-bit input data port, X, in four clock cycles, and the result unloaded in two clock cycles. Two single precision inputs can be loaded in two clock cycles and the result unloaded in a single clock cycle. One or both operands can be stored internally, allowing multiple functions or repeated

operations with a constant to be performed on two operands.

All inputs and outputs are fully registered. All are loaded on each positive-going transition of the clock. Transfers from input registers to the ALU or multiplier array are accomplished with load controls. Unload controls select transfers from the array to the output registers and control tri-stating of the output registers.

A mode register selects optional characteristics that are not often changed, such as the selection of IEEE format, operation timing and rounding modes. The 16-bit mode register is loaded in 4-bit segments from the function input registers.

Arithmetic functions are selected by a 6-bit function control, which is transferred at the same time as the final operand. A 4-bit status output flags arithmetic exceptions and conditions.

#### Pin Definitions

X31-0

32-bit Input/Output Port

S3-0

4-bit status port which indicates execeptions or conditions resulting from floating point operations.

F4-0

5-bit function control port

L3-0

The 4-bit load control is used to specify the site and destination of the data on the X Port and start the instruction.

U

Unload control is used to specify the most or least significant half of the result latch.

CSL-

Load enable; load control loaded only if CSL- is a logic "0"

CSUX-

This signal controls the direction of the internal X1 Bus and serves as the synchronous output enable for the X

Port. CSUX- must *not* be asserted when loading data from the X Port.

CSUS-

Synchronous status output enable

OE-

Asynchronous status and output enable; to activate/deactivate outputs both CSUX- and OE- must be a logic "0"/logic "1" with the proper timing. Status outputs are similarly controlled by OE- and CSUS-.

CLK

System clock; all registers are synchronized to the positive-going edge of the clock.

Vcc

5V power supply for input/output port; all Vcc pins must be connected.

$V_{DD}$

5V power supply for internal circuits; all VDD pins must be connected.

**GND**

Ground; all GND pins must be connected.

## **Block Diagram**

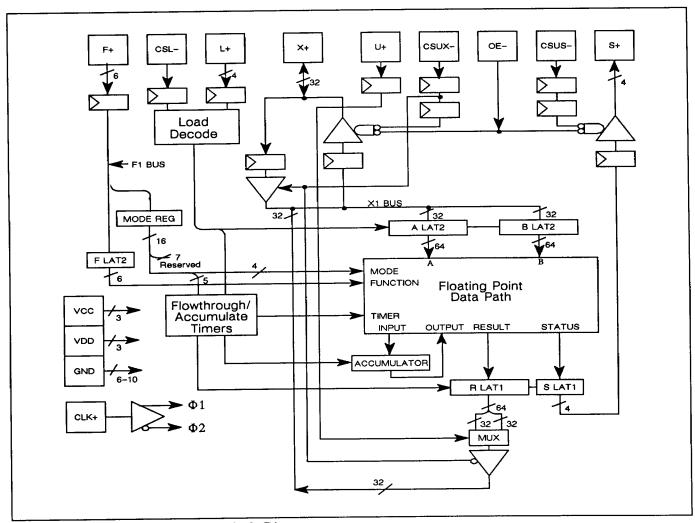

Figure 1. WTL 1164/WTL 1165 Block Diagram

#### NOTATION

The signal names used are described by the data path diagram (see Figure 1). The notation "-" following a signal (i.e., OE-) indicates a negative true signal. The notation "SIGNAL1" indicates a signal that is produced by a single full register from another signal, named "SIGNAL", and "SIGNAL2" indicates a signal produced by a second level of register. A register with no clock signal indicated is clocked unconditionally by the CLK signal, while others may have gated or enabled clocks.

In some cases, half-registers (latches) are used instead of registers. These are marked "LAT1" if they are transparent when the CLK signal is high and latching when CLK is low, or "LAT2" if they are transparent when CLK is low and latching when CLK is high.

Individual bits in a multi-bit signal are numbered from zero, starting with the least significant bit (little-endian).

## Block Diagram, continued

All input signals, with the sole exception of OE-, are synchronized on the rising edge of CLK which, in the tables below, is denoted edge #0. Actions which are taken on the rising edge following the associated input signal are listed under edge #1, and actions taken after

two rising edges are listed under edge #2. Actions which are taken on the falling edge following the associated input signal are listed under edge #0.5, and actions taken after two falling edges are listed under edge #1.5.

## **Specifications**

## ABSOLUTE MAXIMUM RATINGS (Above Which The Useful Life May Be Impaired)

| Supply voltage0.5 to 7.0 V Input voltage0.5 to 5.5 V | Storage temperature range65°C to Lead temperature (10 seconds) | 150°C<br>300°C |

|------------------------------------------------------|----------------------------------------------------------------|----------------|

| Output voltage                                       | Junction temperature                                           |                |

| Operating temperature range (Tcase) -55°C to 125°C   |                                                                |                |

## RECOMMENDED OPERATING CONDITIONS

|                                          | 116        | 34/1165-6 | 0          | 116  | 4/1165-8 | 0    |      |

|------------------------------------------|------------|-----------|------------|------|----------|------|------|

|                                          | COMMERCIAL |           | COMMERCIAL |      |          |      |      |

| PARAMETER                                | MIN        | NOM       | MAX        | MIN  | NOM      | MAX  | UNIT |

| Supply voltage, V cc                     | 4.75       | 5.0       | 5.25       | 4.75 | 5.0      | 5.25 | ٧    |

| Supply voltage, V DD                     | 4.75       | 5.0       | 5.25       | 4.75 | 5.0      | 5.25 | V    |

| Operating temperature, T <sub>CASE</sub> | 0          |           | 80         | 0    |          | 80   | °C   |

#### DC ELECTRICAL CHARACTERISTICS, 1

|                   | PARAMETER                                | TEST CONDITIONS                                                           | MIN | MAX | UNIT | NOTES  |

|-------------------|------------------------------------------|---------------------------------------------------------------------------|-----|-----|------|--------|

| V <sub>iH</sub>   | High-level input voltage                 | $V_{DD}/V_{CC} = MIN$                                                     | 2.0 |     | ٧    |        |

| V <sub>IL</sub>   | Low-level input voltage                  | $V_{DD}/V_{CC} = MIN$                                                     |     | 0.8 | ٧    |        |

| V <sub>OH</sub>   | High-level output voltage                | $V_{DD}/V_{CC} = MIN, I_{OH} = -1.0 \text{ mA}$                           | 2.4 |     | ٧    | ·      |

| V <sub>OL</sub>   | Low-level output voltage                 | $V_{DD}/V_{CC} = MIN, I_{OL} = 4.0 \text{ mA}$                            |     | 0.4 | V    |        |

| I <sub>LI</sub>   | Input leakage current                    | $V_{DD}/V_{CC} = MAX, V_{IN} = 0 \text{ to } V_{CC}$                      |     | 10  | μА   |        |

| ILO               | Output leakage current (output disabled) | $V_{DD}/V_{CC} = MAX$ , $V_{IN} = 0$ or $V_{CC}$                          |     | 10  | μА   |        |

| CIN               | Input capacitance                        | $V_{CC} = MAX, V_{IN} = 0 \text{ to } V_{CC}$                             |     | 5   | рF   | Note 2 |

| Соит              | Output capacitance                       | $V_{CC} = MAX, V_{OUT} = 0 \text{ to } V_{CC}$                            |     | 8   | pF   | Note 2 |

|                   | Clock Input capacitance                  | Vcc = MAX, V <sub>IN</sub> = 0 to Vcc                                     |     | 15  | рF   | Note 2 |

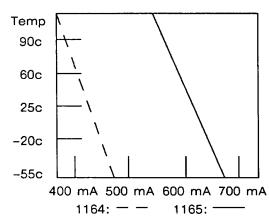

|                   | Supply current, WTL1164                  | V <sub>DD</sub> /V <sub>CC</sub> = MAX; T <sub>CY</sub> = MIN; TTL inputs |     | 600 | mA   | Note 3 |

| l <sub>cc</sub> + | <sub>DD</sub> Supply current, WTL1165    | V <sub>DD</sub> /V <sub>CC</sub> = MAX; T <sub>CY</sub> = MIN; TTL inputs |     | 700 | mA   | Note 3 |

Note 1: Tested from Tcase = 0° C min to 80° C max; Vod and Vcc from 4.75 to 5.25V.

Note 2: Not tested.

Note 3: Worst case power is at 0° C. See Figure 4 for typical power vs. temperature curve.

## WTL 1164/WTL 1165 64-BIT IEEE FLOATING POINT MULTIPLIER/ **DIVIDER AND ALU**

## PRELIMINARY DATA

## Specifications, continued

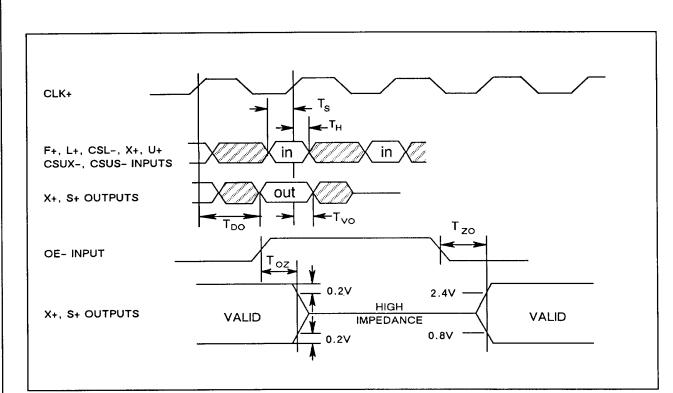

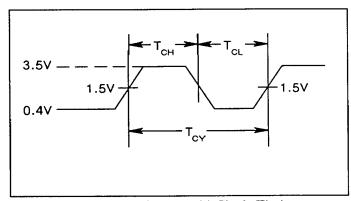

## AC ELECTRICAL CHARACTERISTICS, 1, 4

| <u> </u>                                                                                                                                    |                                                                                                                                        | 1164/1165-60            |            | 165-60                                   | 1164/1     | 165-80                                   |                            |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|------------------------------------------|------------|------------------------------------------|----------------------------|

|                                                                                                                                             | PARAMETER                                                                                                                              | TEST CONDITIONS         | MIN        | MAX                                      | MIN        | MAX                                      | UNIT                       |

| Tcy                                                                                                                                         | Clock cycle time                                                                                                                       | Figure 3                | 60         | DC                                       | 80         | DC                                       | ns                         |

| Тсн                                                                                                                                         | Clock high time                                                                                                                        | Figure 3                | 27         | DC                                       | 35         | DC                                       | ns                         |

| T <sub>CL</sub>                                                                                                                             | Clock low time                                                                                                                         | Figure 3                | 27         | 1000                                     | 35         | 1000                                     | ns                         |

| Ts                                                                                                                                          | Input setup time                                                                                                                       | Figure 2                | 15         |                                          | 15         |                                          | ns                         |

| Тн                                                                                                                                          | Input hold time                                                                                                                        | Figure 2                | 3          |                                          | 2          | *******                                  | ns                         |

| T <sub>DO</sub>                                                                                                                             | Output delay time                                                                                                                      | Figure 2                |            | 35                                       |            | 35                                       | ns                         |

| Tvo                                                                                                                                         | Output valid time                                                                                                                      | Figure 2; Note 6        | 5          |                                          | 3          |                                          | ns                         |

| Toz                                                                                                                                         | Output disable time                                                                                                                    | Figure 2; Notes 5 and 6 | 3          | 35                                       | 3          | 35                                       | ns                         |

| Tzo                                                                                                                                         | Output enable time                                                                                                                     | Figure 2                | 3          | 35                                       | 3          | 35                                       | ns                         |

| T <sub>FL</sub>                                                                                                                             |                                                                                                                                        |                         |            | 240<br>240                               |            | 240<br>240                               | ns<br>ns                   |

| T <sub>AC</sub>                                                                                                                             | T <sub>AC</sub> Accumulation time WTL1164 Floating point multiplier WTL1165 Floating point ALU                                         |                         |            | 120<br>60                                |            | 160<br>80                                | ns<br>ns                   |

| T <sub>NC</sub>                                                                                                                             | Operand encoding time                                                                                                                  | WTL 1164                |            | 60                                       |            | 80                                       | ns                         |

| Top                                                                                                                                         |                                                                                                                                        |                         |            | 240<br>360                               |            | 240<br>400                               | ns<br>ns                   |

|                                                                                                                                             | WTL1165 Floating p<br>32-bit divide<br>64-bit divide<br>all other 32-bit fu<br>all other 64-bit fu                                     | unctions                |            | 1740<br>3480<br>240<br>240               |            | 2240<br>4560<br>240<br>240               | ns<br>ns<br>ns             |

| T <sub>LA</sub> Total latency (using T <sub>CY</sub> min) WTL1164 Floating point multiplier 32-bit multiply 64-bit minimum latency multiply |                                                                                                                                        |                         | 420<br>600 |                                          | 480<br>700 | ns<br>ns                                 |                            |

|                                                                                                                                             | WTL1165 Floating p<br>32-bit divide<br>64-bit divide<br>32-bit single ope<br>64-bit single ope<br>32-bit double op<br>64-bit double op | rand instructions       |            | 1920<br>3780<br>360<br>420<br>420<br>540 |            | 2480<br>4900<br>400<br>480<br>480<br>640 | ns<br>ns<br>ns<br>ns<br>ns |

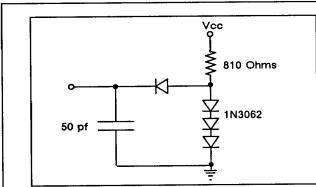

Note 4: All transitions except Toz are measured at 1.5V level, as shown in Figure 2, with TTL inputs of 0.4V and 3.5V. The test load in Figure 5 is used.

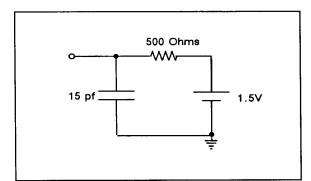

Note 5: The test load in Figure 6 is used.

Note 6: Guaranteed but not tested.

Specifications subject to change without petics.

Specifications subject to change without notice.

## I/O Chracteristics

Figure 2. WTL 1164/WTL 1165 Input/Output Timing

Figure 3. WTL 1164/WTL1165 Clock Timing

Figure 4. Typical I cc + I DD vs. Temperature

## I/O Chracteristics, continued

Figure 5. Normal Load Circuit for Delay Measurements

Figure 6. Toz Measurement Circuit

## Method of Operation

## LOAD CONTROLS

The CSL- and L input signals control the loading of operands into the on-chip registers and into the arithmetic path. The signals also control the loading of operating modes into on-chip mode registers from the 6-bit function code bus.

Using CSL- and L, data presented on the external bus, X, may be written into the on-chip registers, A and B, where they pass directly into the arithmetic unit.

The CSL- signal, if de-asserted (1), causes no load operations to be performed, regardless of the state of the L signal. Load operations are performed only if the CSL- signal is asserted.

#### LOAD NOTES

CSL- is often used as a chip select to allow the sharing of the L and F fields. An inverter can be used to generate CSL- for the other device if the L Field specifies a NOP when no loading is desired.

If Lo is set, indicating a function is to be started, the F Register (FREG) is loaded and an operation is initiated. This also resets the pipeline advance timer and the accumulator advance timer.

If Lo and CSL- are both asserted while an operation is in progress, it will cause that operation to abort but will not start the new operation. The result of an aborted operation is undefined.

For the conversion of integer to single or double precision functions, the 32-bit integer operand must be loaded into the A Operand Register with the LAL (#12) or LALF (#13) load commands.

Divide uses the A Operand Register for intermediate values. The A Register must be reloaded prior to starating another instruction following a divide operation.

Single precision loads modify both halves of the A or B register.

## Method of Operation, continued

| L <sub>3</sub> L <sub>2</sub> L <sub>1</sub> L <sub>0</sub> | Mnemonic                  | EDGE #0.5                                                                                               |                     |

|-------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------|---------------------|

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                     | LNOP<br>LF                | V1 > P [gingle]                                                                                         | NOP<br>F1 → FREG    |

| 0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0         | LBS<br>LBSF<br>LBL        | X1 → B [single]<br>X1 → B [single]<br>X1 → B [LSW double]<br>X1 → B [LSW double]<br>X1 → B [MSW double] | F1 → FREG           |

| 0 1 0 1 0 1 0 1 1 1                                         | LBLF<br>LBM               | X1 → B [LSW double] X1 → B [MSW double] X1 → B [MSW double]                                             | F1 → FREG F1 → FREG |

| 1 0 0 0                                                     | LBMF<br>LMODE             | X1 > B [Mevi dedoie]                                                                                    | LOAD MODE           |

| 1 0 1 0                                                     | - reserved<br>LAS<br>LASF | $X1 \rightarrow A \text{ [single]}$<br>$X1 \rightarrow A \text{ [single]}$                              | F1 → FREG           |

| 1 1 0 0 1 1 1 1 0                                           | LAL<br>LALF<br>LAM        | X1 → A [LSW double]<br>X1 → A [LSW double]<br>X1 → A [MSW double]                                       | F1 → FREG           |

| i i i i                                                     | LAMF                      | X1 → A [MSW double]                                                                                     | F1 → FREG           |

Table 1. L Input

#### **UNLOAD CONTROLS**

The unload controls, U, CSUX- and CSUS-, select the data to be presented on the external bus, X, and the status bus, S. The U signal controls whether the most significant word or the least significant word is sent to the X Bus. Single precision floating point results are unloaded by selecting the most significant word, while

results in integer format are unloaded by selecting the least significant word.

The CSUS- and CSUX- signals control tri-stating of the S and X buses, respectively, in a synchronous fashion. The OE- signal controls tri-stating of both the S and X Buses and is a fully asynchronous signal. In the chart below, X1 refers to the X1 Bus shown in Figure 1.

| CSUS - | CSUX - | U | Mnemonic | EDGE #0.5          | EDGE #1                 |                    |

|--------|--------|---|----------|--------------------|-------------------------|--------------------|

| 0      | 0      | 0 | ULST     | LSW result → X1    | STREG1 $\rightarrow$ S, | $X1 \rightarrow X$ |

| 0      | 0      | 1 | UMST     | MSW result → X1    | STREG1 $\rightarrow$ S, | $X1 \rightarrow X$ |

| 0      | 1      | X | UST      | $X \rightarrow X1$ | STREG1 $\rightarrow$ S, | X tri-stated       |

| 1      | 0      | 0 | UL       | LSW result → X1    | S tri-stated,           | $X1 \rightarrow X$ |

| 1      | 0      | 1 | UM       | MSW result → X1    | S tri-stated,           | $X1 \rightarrow X$ |

| 1      | 1      | X | UNOP     | $X \rightarrow X1$ | S tri-stated,           | X tri-stated       |

Table 2. U Input

## **FUNCTION CONTROLS**

The function controls select the operation to be performed by the floating point units. Each chip has a separate set of function code definitions.

The F signal is received on each clock edge and buffered as the F1 Bus. An operation is started when ordered by the Lo signal. Starting an operation loads F1  $\rightarrow$  F LAT2, and resets the flowthrough and accumulate timers.

In the tables below, F32 denotes a single precision floating point operand or result; F64 denotes a double precision value. F32/64 represents either a single or double precision floating point operand. W32 and W64 denote single and double precision wrapped, normalized operands and results. U32 and U64 denote single and double precision unrounded, wrapped, normalized operands and results. I32 represents a 32-bit integer value.

#### WTL 1164/WTL 1165 64-BIT IEEE FLOATING POINT MULTIPLIER/ DIVIDER AND ALU

#### PRELIMINARY DATA

## Method of Operation, continued

When two operands are indicated, the A operand is given on the left and the B operand on the right. When only one operand is indicated, it must be loaded into the A Operand Register.

When a double precision result is indicated, operands may be either single precision or double precision or mixed single and double precision. The load controls indicate the precision of the operands as they are loaded. Mixed precision operations must be loaded in the specified loading sequence (figures 7, 8 and 14).

If an instruction is started when another instruction is in progress, in either the multiplier or ALU, both instructions are corrupted. While divide operations are in progress a new instruction may be started by first starting some arbitrary instruction (killing both instructions), waiting three cycles, then beginning the third instruction.

Function Controls For Floating Point Multiplier (WTL 1164)

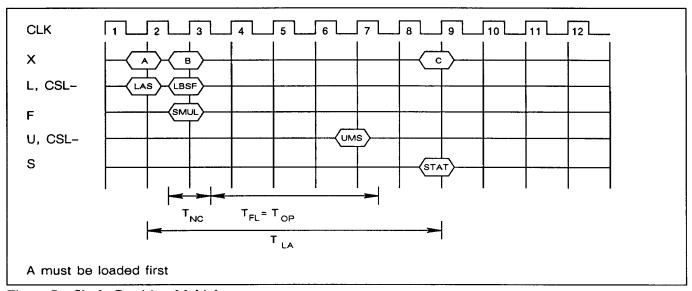

For the multiplier, the timing of the function is determined by the precision of the B operand. When the B operand is single precision, the multiplication is performed in the flowthrough operation time, TFL; when the B operand is double precision, the time is increased by the accumulate time, Tac.

The floating point multiplier uses functions provided on the floating point ALU for the handling of denormalized operands and results, significantly increasing multiplier performance and reducing system cost. A mode bit is provided to select whether full handling of denormalized operands is required.

In IEEE mode, denormalized operands are detected in the multiplier and exceptions are generated when they are found, indicating which operands are denormalized. The original operands may then be sent to the floating point ALU, where the wrap function normalizes the operands and extends the range of the exponent. The modified operands may then be multiplied, using function codes F2-0 = #2 through #7 in the floating point multiplier. In "FAST" mode, denormalized operands are treated as zero.

Whether or not the operands are denormalized, the multiplier may also produce a number whose exponent is too small to be represented as a normalized floating point value. In IEEE mode, one of the exceptions, Underflow or Underflow & Inexact, is generated, and the value returned is a normalized number with extended range and without rounding. This value may be converted to a denormalized number or zero value by using the Unwrap Exact or Unwrap Inexact functions of the floating point ALU. In "FAST" mode, these results are given zero values and the Underflow or Underflow & Inexact exception is generated.

Certain restrictions are imposed on the timing with which operands are loaded into the WTL 1164 floating point multiplier. The A operand is internally encoded into a more usable form immediately after the operand is loaded. The encoded A operand is loaded into an internal register when a multiplication function is indicated by the Lo signal. The time required for the encoding is TNC, which is normally no greater than the time required to load the B operand. Thus, if the A operand is loaded first, followed by the B operand, the multiplication function can begin immediately upon loading the B operand. If the B operand must be loaded first, an additional cycle is required before starting the operation.

In some applications, a series of multiplications may be performed with one of the two operands held constant. Ideally, in order to maximize performance, this constant operand is the A operand, so each multiplication can begin immediately upon loading the B operand.

## Method of Operation, continued

| F <sub>2</sub> F <sub>1</sub> F <sub>0</sub>                | Operation | Description                                                                                                                                                                           |

|-------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | F32       | double multiply single multiply, A wrapped double multiply, A wrapped single multiply, B wrapped double multiply, B wrapped single multiply, B wrapped single multiply, A & B wrapped |

| F <sub>5</sub> F <sub>4</sub> F <sub>3</sub>                | Operation                                                                                  | Description                                                                                                                                                                           |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | A * B<br> A  *  B <br> A *  B <br> A  *  B <br> -  A  *  B <br> -  A  *  B <br> -  A  *  B | multiply B times magnitude of A A times magnitude of B magnitude of A times B multiply and negate B times negative value of A A times negative value of B negative value of A times B |

Table 3. Function Controls for Floating Point Multiplier

#### Function Controls For Floating Point ALU (WTL 1165)

The function controls for the WTL 1165 are shown in Table 4. Mixed precision operations and divide operations may generate one of the denormalized input exceptions; all other operations can handle denormalized operands directly without the exception.

When a DNRM exception is encountered in a mixed-mode operation, the DNRM input must first be converted to double precision before the instruction can be re-started.

Like the WTL 1164, the WTL 1165 may produce a result whose exponent is too small to be represented as a normalized floating point value. When this result appears in IEEE mode, one of the exceptions Underflow or Underflow & Inexact is generated and the value returned is a normalized number with extended range and without rounding. This value may be converted to a denormalized number or zero value by

using the Unwrap Exact or Unwrap Inexact functions of the floating point ALU. In "FAST" mode, these results are given zero values and the Underflow or Underflow & Inexact exception is generated.

When performing the divide function in IEEE mode, denormalized operands are detected and exceptions are generated when they are found, indicating which operands are denormalized. The operands may then be loaded into the A operand of the floating point ALU, where the wrap function normalizes the operand and extends the range of the exponent. The modified operands may then be divided using function codes F5-0 = #14-15, #22-23, #30-31 in the floating point ALU. In "FAST" mode, denormalized operands are treated as zero, yielding a zero or infinite result and no denormalized operand exceptions. A divide-by-zero exception will occur, however, if a denormalized operand is used as a divisor in "FAST" mode.

# Method of Operation, continued

| F <sub>5</sub> F <sub>4</sub> F <sub>3</sub> F <sub>2</sub> F <sub>1</sub> F <sub>0</sub>                                                                                                                                                                        | Operation                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0 0 0 0 0 (0)<br>0 0 0 0 0 1 (1)<br>0 0 0 0 1 0 (2)<br>0 0 0 0 1 1 (3)<br>0 0 0 1 0 0 (4)<br>0 0 0 1 1 0 (6)<br>0 0 0 1 1 1 (7)<br>0 0 1 0 0 0 (8)<br>0 0 1 0 0 1 (9)<br>0 0 1 0 1 0 (10)<br>0 0 1 0 1 1 (11)                                                | F32                                                                                                                                                                                                                                                                                                                              | single subtract double subtract single magnitude of difference double magnitude of difference single subtract magnitudes double subtract magnitudes single divide double divide single negate plus zero double negate plus zero                       |

| 0 0 1 1 0 0 (12)<br>0 0 1 1 0 1 (13)<br>0 0 1 1 1 0 (14)<br>0 0 1 1 1 1 (15)<br>0 1 0 0 0 0 (16)<br>0 1 0 0 0 1 (17)<br>0 1 0 0 1 0 (18)<br>0 1 0 0 1 1 (19)<br>0 1 0 1 0 1 (21)<br>0 1 0 1 1 0 (22)<br>0 1 0 1 1 1 (23)<br>0 1 1 0 0 1 (25)<br>0 1 1 0 1 0 (26) | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                             | single divide, A wrapped double divide, A wrapped single add double add single magnitude of sum double magnitude of sum single add magnitude double add magnitude single divide, B wrapped double divide, B wrapped single plus zero double plus zero |

| 0 1 1 0 1 1 (27)<br>0 1 1 1 0 0 (28)<br>0 1 1 1 0 1 (29)<br>0 1 1 1 1 0 (30)<br>0 1 1 1 1 1 (31)<br>1 0 0 0 0 0 (32)<br>1 0 0 0 0 1 (33)<br>1 0 0 0 1 0 (34)                                                                                                     | F32  + 0 → F32/U32<br> F32/F64  + 0 → F64/U64<br>W32 ÷ W32 → F32/U32<br>W32/W64 ÷ W32/W64 → F64/U64<br>Compare F32 - F32<br>Compare F32 / F64 - F32 / F64                                                                                                                                                                        | single absolute value<br>double absolute value<br>single divide, A & B wrapped<br>double divide, A & B wrapped<br>single compare<br>double compare                                                                                                    |

| 1 0 0 0 1 1 (35)<br>1 0 0 1 0 0 (36)<br>1 0 0 1 0 1 (37)<br>1 0 0 1 1 0 (38)                                                                                                                                                                                     | Compare  F32  -  F32 <br>Compare  F32 / F64  -  F32 / F64                                                                                                                                                                                                                                                                        | single compare magnitude<br>double compare magnitude                                                                                                                                                                                                  |

| 1 0 0 1 1 1 (39)<br>1 0 1 0 0 0 (40)<br>1 0 1 0 0 1 (41)<br>1 0 1 0 1 0 (42)<br>1 0 1 0 1 1 (43)<br>1 0 1 1 0 0 (44)<br>1 0 1 1 0 1 (45)                                                                                                                         | Compare F32 - 0<br>Compare F32 / F64 - 0                                                                                                                                                                                                                                                                                         | single compare with zero<br>double compare with zero                                                                                                                                                                                                  |

| 1 0 1 1 0 1 (49)<br>1 0 1 1 1 0 (46)<br>1 0 1 1 1 1 (47)<br>1 1 0 0 0 0 (48)<br>1 1 0 0 0 1 (49)<br>1 1 0 0 1 0 (50)<br>1 1 0 0 1 0 (52)<br>1 1 0 1 0 1 (53)<br>1 1 0 1 1 0 (54)<br>1 1 0 1 1 (55)                                                               | $\begin{array}{c} \text{U32} \rightarrow \text{F32}  (\text{Exact}) \\ \text{U64} \rightarrow \text{F64}  (\text{Exact}) \\ \text{F32} \rightarrow \text{W32} \\ \text{F64} \rightarrow \text{W64} \\ \text{U32} \rightarrow \text{F32}  (\text{Inexact}) \\ \text{U64} \rightarrow \text{F64}  (\text{Inexact}) \\ \end{array}$ | single unwrap exact value<br>double unwrap exact value<br>single wrap denormalized value<br>double wrap denormalized value<br>single unwrap inexact value<br>double unwrap inexact vlaue                                                              |

Table 4. Function Controls for Floating Point ALU

## Method of Operation, continued

| F <sub>5</sub> F <sub>4</sub> F <sub>3</sub> F <sub>2</sub> F <sub>1</sub> F <sub>0</sub>                                                  | Operation                                                                                                                                                | Description                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 1 1 0 0 0 (56)<br>1 1 1 0 0 1 (57)<br>1 1 1 0 1 0 (58)<br>1 1 1 0 1 1 (59)<br>1 1 1 1 0 0 (60)<br>1 1 1 1 1 0 1 (61)<br>1 1 1 1 1 1 (63) | $132 \rightarrow F32$<br>$132 \rightarrow F64$<br>$132 \rightarrow F32$<br>$132 \rightarrow F64$<br>$F64 \rightarrow F32 / U32$<br>$F32 \rightarrow F64$ | single convert to integer<br>double convert to integer<br>single float<br>double float<br>convert double to single<br>convert single to double |

Table 4. Function Controls for Floating Point ALU, continued

## **Mode Controls**

The mode controls are not directly loaded from external pins. Instead, when the load mode command is presented on the L signal, F5-4 selects one of four

mode control segments to be loaded with the signal  $F_{3-0}$ , according to the following table.

| F <sub>5</sub> F <sub>4</sub>            | EDGE #0                                                                                                                 | EDGE #0.5                                                                                                                                                                                                                                                             |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 (0)<br>0 1 (1)<br>1 0 (2)<br>1 1 (3) | $ \begin{array}{ccc} F \rightarrow & F1 \\ F \rightarrow & F1 \\ F \rightarrow & F1 \\ F \rightarrow & F1 \end{array} $ | $\begin{array}{cccc} F1_{3\text{-}0} & \longrightarrow & MODE_{3\text{-}0} \\ F1_{3\text{-}0} & \longrightarrow & MODE_{7\text{-}4} \\ F1_{3\text{-}0} & \longrightarrow & MODE_{11\text{-}8} \\ F1_{3\text{-}0} & \longrightarrow & MODE_{15\text{-}12} \end{array}$ |

Mode controls must not be altered while a floating point function is in progress.

#### "FAST"/IEEE FORMAT MODE CONTROL

MODEo controls the floating point format used for all operations and the manner in which the denormalized

operands and results are handled, according to the following table.

| MODE <sub>0</sub> | Function                                                                                                     |             |

|-------------------|--------------------------------------------------------------------------------------------------------------|-------------|

| 0                 | Multiplier and ALU generate denormalized operand exceptions and produce UNRM values on underflow exceptions. | (IEEE mode) |

| 1                 | Multiplier and ALU flush denormalized operands to zero and round underflow results to zero.                  | (FAST mode) |

#### ROUNDING MODE CONTROL FOR ALU FIX FUNCTION

| MODE <sub>1</sub> | Function                                                   |

|-------------------|------------------------------------------------------------|

| 0                 | Round according to default rounding mode (MODE 3-2)        |

| 1                 | Round toward zero, regardless of the default rounding mode |

|                   |                                                            |

## Mode Controls, continued

#### ROUNDING MODE CONTROL

MODE3-2 control the IEEE rounding mode for all operations, except for the ALU functions Convert

Single to Integer and Convert Double to Integer, according to the following table.

| MODE3-2 | Function                                                |  |

|---------|---------------------------------------------------------|--|

| 00      | Round toward nearest value or even significand if a tie |  |

| 01      | Round toward zero                                       |  |

| 10      | Round toward positive infinity                          |  |

| 11      | Round toward negative infinity                          |  |

## FLOWTHROUGH TIMER CONTROL

MODE7-5 allow the number of clock cycles required to meet the flowthrough time TFL to be selected using clock periods other than 60 ns. The value for TFL which should be used is specified on page 5 under "AC ELECTRICAL CHARACTERISTICS". Using 240 ns for TFL and the recommended clock speed of 60 ns, the value, k, which should be loaded into MODE7-5 is

three. To determine k for other clock periods or flowthrough times, the following formula may be used where I means round up to the next integer greater than or equal to the result:

MODE 7-5 =

$$\int (T_{FL} \div Clock Period) - 1$$

| Clock Frequency (MHz) | ock Frequency (MHz) Clock Period (ns) |   | MODE 7-5 |

|-----------------------|---------------------------------------|---|----------|

| 20.0                  | 50                                    | 5 | 100 (4)  |

| 16.7                  | 60                                    | 4 | 011 (3)  |

| 14.3                  | 70                                    | 4 | 011 (3)  |

| 12.5                  | 80                                    | 3 | 010 (2)  |

| 8.33                  | 120                                   | 2 | 001 (1)  |

The flowthrough timer should never be set to 0.

#### ACCUMULATE TIMER CONTROL

If the B operand on the WTL 1164 is single precision, the multiplication is performed as a flowthrough operation, but if the B operand is double precision two passes must be made through the multiplier array. After the first pass the partial results of the multiplication are held in an accumulate register. These partial results are added to the results of the second pass to form the unrounded product. The minimum time required for the first pass through the array is called the accumulation time. For a given clock frequency the time taken for this accumulation operation is controlled by MODE11-10. MODE11-10 control when the Internal Accumulator Register in the multiplier is clocked. Loading a value, k, into

MODE<sub>11-10</sub> causes the accumulator to be clocked k + 1 cycles after an operation is started.

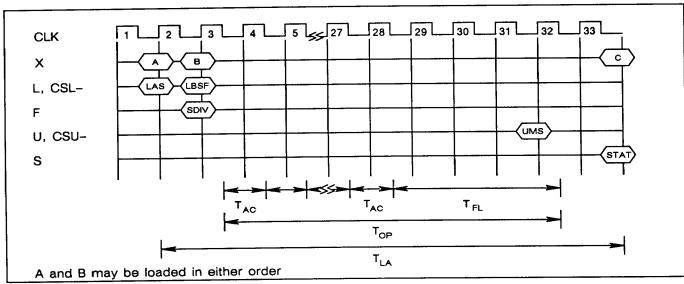

Most functions of the WTL 1165 are performed as a flowthrough operation, except for divide operations. Divide operations on the WTL 1165 are performed in a bit-sequential fashion and require 25 iterations for a single precision divide and 54 iterations for a double precision divide. The time taken for each iteration is controlled by MODE11-10. MODE11-10 control the rate at which the internal accumulator register in the divide circuitry is clocked. Loading a value, k, into MODE11-10 causes the accumulator to be clocked every k + 1 cycles after the start of a divide operation.

## Mode Controls, continued

In general, the value used for MODE11-10 will not be the same for both chips. The value for Tac which should be used is specified on page 5 under "AC ELECTRICAL CHARACTERISTICS". The formula for calculating the value to be loaded into MODE11-10 is given below:

The value which should be loaded into MODE11-10 for the WTL 1164 using 120 ns for Tac and a 60 ns clock is one. Values for other clock frequencies are shown in the table below:

Where \( \) means round up to the next integer greater than or equal to the result.

| Clock Frequency (MHz)                | Clock Period (ns)           | 「TAC ÷ Clock Period        | MODE 11-10                                     |

|--------------------------------------|-----------------------------|----------------------------|------------------------------------------------|

| 20.0<br>16.7<br>14.3<br>11.1<br>8.33 | 50<br>60<br>70<br>90<br>120 | 3<br>2<br>2<br>2<br>2<br>1 | 10 (2)<br>01 (1)<br>01 (1)<br>01 (1)<br>00 (0) |

The value which should be loaded into MODE11-10 for the WTL 1165 using 60 ns for Tac and a 60 ns clock is

zero. Values for other clock frequencies are shown in the table below:

| Clock Frequency (MHz) | Clock Period (ns) | 「TAC ÷ Clock Period | MODE 11-10 |

|-----------------------|-------------------|---------------------|------------|

| 20.0                  | 50                | 2                   | 01 (1)     |

| 16.7                  | 60                | 1                   | 00 (0)     |

| 14.3                  | 70                | 1                   | 00 (0)     |

| 11.1                  | 90                | 1                   | 00 (0)     |

| 8.33                  | 120               | 1                   | 00 (0)     |

After the final firing of the accumulate timer on either the WTL 1164 or WTL 1165, the flowthrough timer is started, terminating the operation after the flowthrough

timer expires. Operation timing can thus be determined from the following formulae.

| Operation                                                                                                                                                                      | Time required in cycles                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Multiply, B operand is single precision Multiply, B operand is double precision Divide, result is single precision Divide, result is double precision Other WTL1165 operations | T <sub>FL</sub> T <sub>AC</sub> + T <sub>FL</sub> 25 * T <sub>AC</sub> + T <sub>FL</sub> 54 * T <sub>AC</sub> + T <sub>FL</sub> T <sub>FL</sub> |

#### RESERVED MODE CONTROL BITS

MODE<sub>15-12</sub>, MODE<sub>9-8</sub> and MODE<sub>4</sub> on the floating point ALU chip and the floating point multiply chip are currently reserved for future definition. These mode

control bits should be set to zero to assure compatibility with future derivatives of the WTL 1164/1165.

# WTL 1164/WTL 1165 64-BIT IEEE FLOATING POINT MULTIPLIER/DIVIDER AND ALU

## PRELIMINARY DATA

#### Result Status

The S Bus indicates any exceptions or conditions that result from operations performed by the floating point units. The status bits associated with an operation have the same timing as the results. The S Bus is controlled by the CSUS- control, which causes the S Bus to be driven two clock cycles after CSUS is asserted. For

comparison operations, the S Bus indicates the condition resulting from the comparison; for all other operations, the S Bus indicates exception status arising from the associated operation. For all operations, the S Bus has the following meanings.

| S 3 S 2 S 1 S 0                                              | Comparison Condition               | Exception Status                                                                                                               |

|--------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0 0 (0)<br>0 0 0 1 (1)<br>0 0 1 0 (2)<br>0 0 1 1 (3)     | Equal<br>Less than<br>Greater than | Result = +0 or -0, exact  Result = +infinity or -infinity, exact  Result finite and ≠ 0, exact  Result finite and ≠ 0, inexact |

| 0 1 0 0 (4)<br>0 1 0 1 (5)<br>0 1 1 0 (6)<br>0 1 1 1 (7)     |                                    | <ul> <li>not used</li> <li>Overflow &amp; inexact</li> <li>Underflow</li> <li>Underflow &amp; inexact</li> </ul>               |

| 1 0 0 0 (8)<br>1 0 0 1 (9)<br>1 0 1 0 (10)<br>1 0 1 1 (11)   |                                    | Operand A is Denormalized<br>Operand B is Denormalized<br>Operands A & B are Denormalized<br>Divide by Zero                    |

| 1 1 0 0 (12)<br>1 1 0 1 (13)<br>1 1 1 0 (14)<br>1 1 1 1 (15) | Unordered                          | Operand A is NaN<br>Operand B is NaN<br>Operands A & B are NaN<br>Invalid Operation                                            |

Exception status signals #0-#3 indicate normal completion of the operation. The specific value of the status signal indicates the type of result produced, either zero, non-zero or infinity as well as exact or inexact. Signals #0-#2 indicate an exact result, as defined by the IEEE standard. Signals #3, #5, #6 and #7 indicate an inexact result. While #6 does not imply inexact directly, the result after unwrapping may be exact or inexact and the status bits correctly indicate exactness at the conclusion of the unwrap operation.

Signals #6 and #7 have special meaning in IEEE mode. These signals indicate the result is smaller than the minimum magnitude normalized number representable in the specified format and a UNRM value is presented as a result. This value should be converted to a legal

denormalized number by the Unwrap Exact (for signal #6) or Unwrap Inexact (for signal #7) functions of the floating point ALU. The exception status indicated by the ALU at the conclusion of the unwrap operation, either #6 or #7, properly indicates the exactness of the result.

Status numbers eight through 11 signify deneormalized input values (DIN) in IEEE mode. Status numbers 12 through 15 signify invalid operations (INV) and source NaNs.

Under certain conditions, multiple exceptions can occur. These exceptions may be resolved with the following priority table, where higher-priority exceptions will mask lower-priority exceptions.

#### Result Status, continued

| Priority          | Exception                                                                                                                                                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Highest<br>Lowest | Operands A & B are NaN Operand A is NaN Operand B is NaN Invalid Operation Divide by Zero Operands A & B are denormalized Operand A is denormalized Operand B is denormalized Underflow & inexact Underflow Overflow & Inexact Result is finite and \$\igcream 0\$, inexact |

## **Timing**

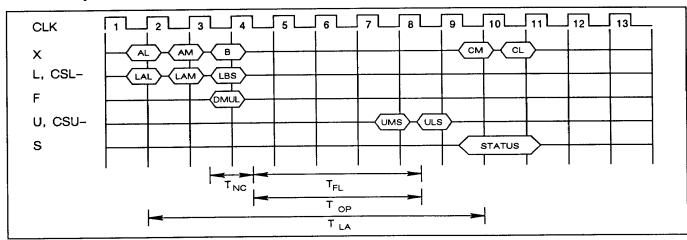

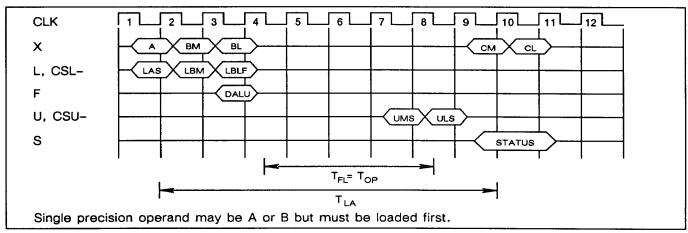

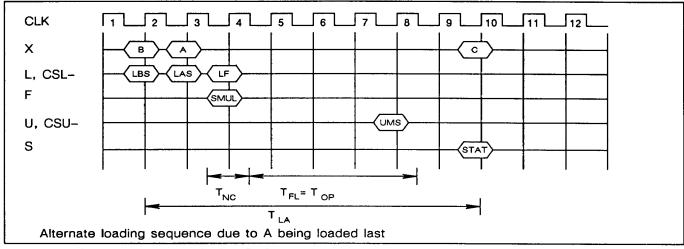

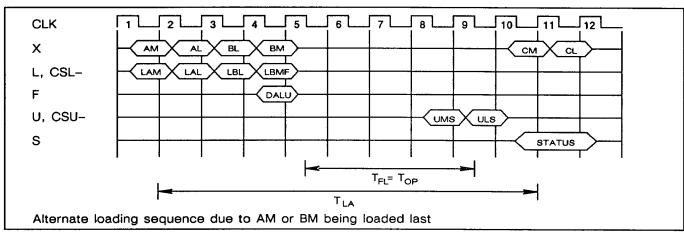

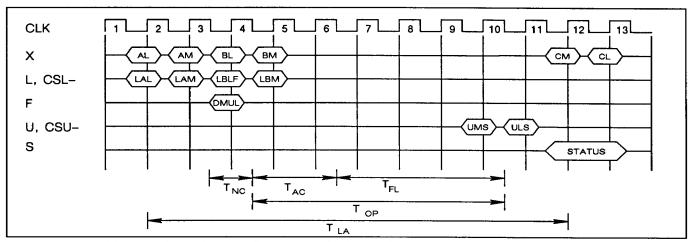

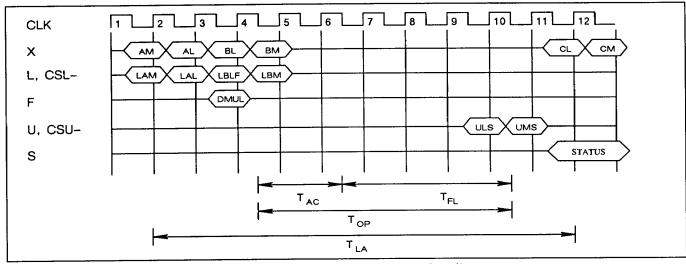

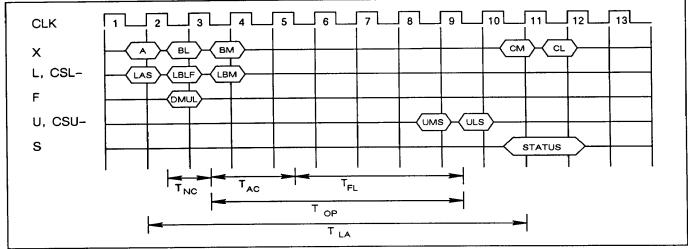

The WTL 1164 and WTL 1165 have very flexible loading controls to optimize loading order for total system performance. Figures 3 through 11 show loading sequences which minimize flowthrough times and are the preferred loading sequences. Figures 15 and 16 show loading sequences which are also valid but incur somewhat longer flowthrough times. While all of the loading sequences shown are guaranteed, restricting the loading order to the preferred loading sequences will minimize timing changes when using

higher clock rates on future WTL 1164/1165 compatable devices.

#### PRECISION PREFERRED LOADING SEQUENCES

To conform to the preferred loading sequence, the loading order must be followed except where indicated. Other sequences may still be acceptable (see alternate loading sequences) but minor timing changes may be required for use with future WTL 1164/1165 family devices at higher clock speeds.

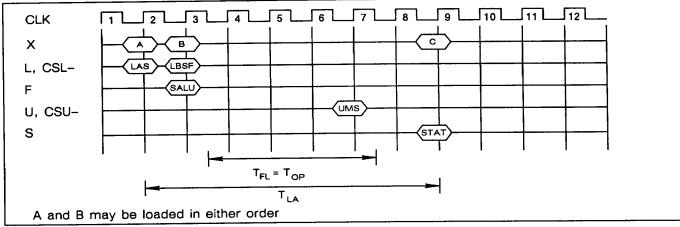

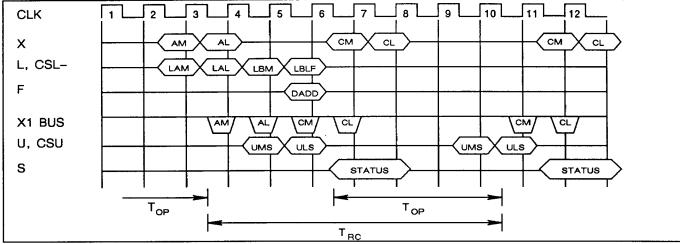

Figure 7. Single Precision Multiply

## Timing, continued

Figure 8. Single Precision Divide

Figure 9. Single Precision ALU Operation

# Timing, continued

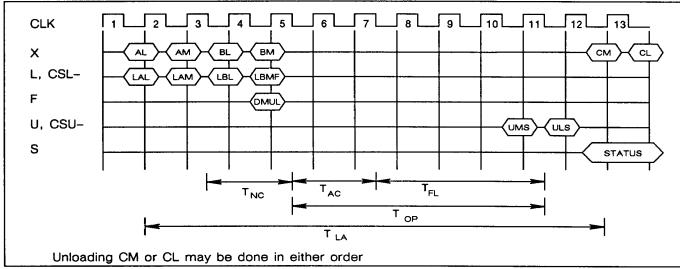

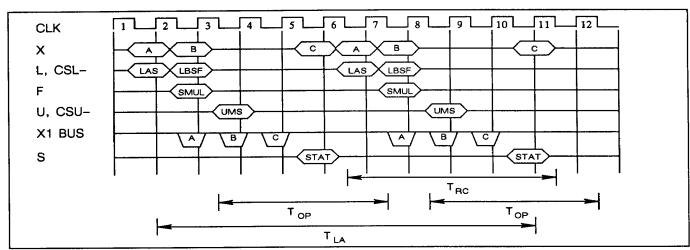

Figure 10. Double Precision Multiply

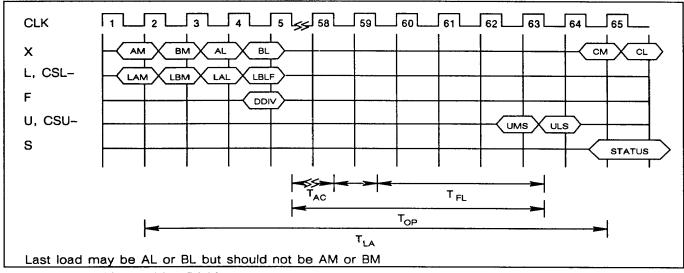

Figure 11. Double Precision Divide

## Timing, continued

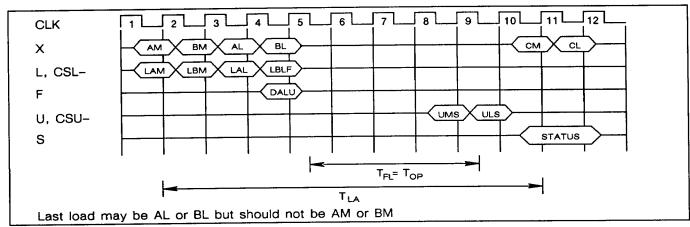

Figure 12. Double Precision ALU Operation

## MIXED-MODE LOADING SEQUENCES

When operating with mixed single and double precision operands, the loading order is especially important. Special values such as zero, infinity and denormalized numbers require conversion from single to double

precision values before the operation can be completed. For that reason, mixed-mode operations must be loaded as specified below.

Figure 13. Mixed-mode Minimum Latency Multiply

# Timing, continued

Figure 14. Mixed-mode ALU Operation

#### ALTERNATE LOADING SEQUENCES

Alternate loading sequences are those which cause flowthrough or encode times to be greater than the preferred loading sequences. Except for mixed-mode, operands may be loaded in any order. Alternate loading sequences are guaranteed by the TFL and TNC specifications but may not be optimum. mixed-mode operands must be loaded in the order specified by figures 13 and 14.

Figure 15. Single Precision Multiply, B Operand First

## Timing, continued

Figure 16. Double Precision ALU Operation, MSW Loaded Last

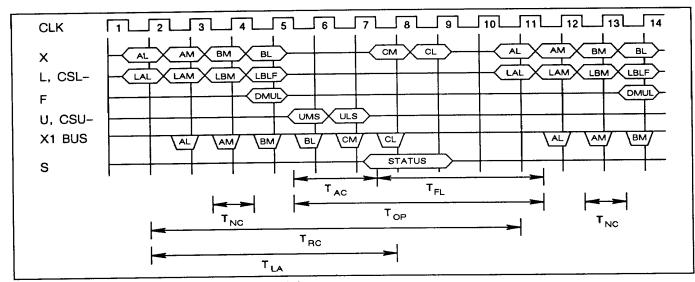

#### OPTIMIZING FLOATING POINT PERFORMANCE

On the WTL 1164, if the least significant half of the B operand is loaded first, the floating point multiplication can be started before loading the most significant half of the B operand. (See figures 17, 18 and 19.) The most significant half must be loaded on the following cycle and the cycle time must be less than the

accumulate time, Tac. This is possible because the initial accumulation operation requires only the least significant word of the B operand. The preferred loading order for the A operand is LSW followed by MSW.

Figure 17. Double Precision Minimum Latency Multiply, Preferred Loading

## Timing, continued

Figure 18. Double Precision Minimum Latency Multiply, Alternate Loading

Figure 19. Alternate Mixed Mode Multiply

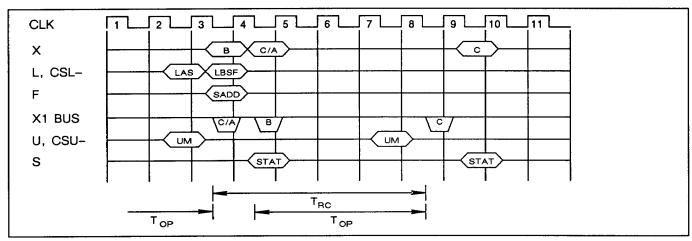

The WTL 1164/1165 contain a result latch at the end of the floating point hardware, allowing results to be loaded directly into one or both of the operand registers (a chained operation) or to start another operation before unloading the result (a pipelined operation).

Results may be chained from a result register back to an operand register by selecting both a load and unload operation on the same clock cycle. The result is passed onto the internal bus and then clocked into the indicated operand register. Normally, the result is also presented on the X Bus on the next clock cycle, which can be useful for ensuring that sufficient internal state is retained externally for aborting and later resuming

an operation of this kind. If avoiding driving the X Bus is desirable, it can be tri-stated by bringing the OE- pin to an inactive (high) level. The time for a series of operations where the result is chained back to one of the operand registers, and another operand is loaded from the X Bus may be calculated as:

$$T_{RC} = T_{CY} + T_{OP}$$

For single precision operations (see Figure 20), and for double precision operations (see Figure 21), the time for each chained operation is:

$$T_{RC} = 3 * T_{CY} + T_{OP}$$

## Timing, continued

Figure 20. Single Precision Chained Add Operation

Figure 21. Double Precision Chained Add Operation

## Timing, continued

The WTL 1164/1165 may be used in a pipelined fashion by loading new operands and starting a second operation before unloading the result of the previous operation. This previous result must be unloaded by selecting unload operations immediately after loading the final operand for the second operation. Due to the one cycle delay between the external X Bus and the internal X1 Bus in each direction, two cycles will elapse before the result appears on the bus. In order to assure that sufficient time to unload the result before the completion of the next operation reloads the result register, Tor must be at least 3\*Tcr for single precision results and at least 4\*Tcr for double precision results. The effective pipeline rate can be calculated from the formula:

$$T_{BC} = max (T_{CY} + T_{OP}, 5 * T_{CY})$$

For single precision operations (see Figure 22), and for double precision operations (see Figure 23), the effective pipeline rate is:

$$T_{RC} = max (3 * T_{CY} + T_{OP}, 8 * T_{CY})$$

If a double precision multiply is performed when loading the least-significant B operand first, the effective pipeline rate is:

$$T_{RC} = max (2 * T_{CY} + T_{OP}, 8 * T_{CY})$$

Note that Top must be at least 4\*Tcy for this operation.

Figure 22. Single Precision Pipelined Multiply

## Timing, continued

Figure 23. Double Precision Pipelined Multiply

# USING FASTER AND SLOWER CLOCK RATES

Because the WTL 1164 and WTL 1165 use both clocked and unclocked logic in the arithmetic data path units, certain optimizations can be made when the parts are operated with clock rates that differ from the

standard maximum clock rate. This permits greater performance in applications where the standard clock rate cannot be easily maintained.

## **Application Note**

#### WEITEK FLOATING POINT COPROCESSOR INTERFACE

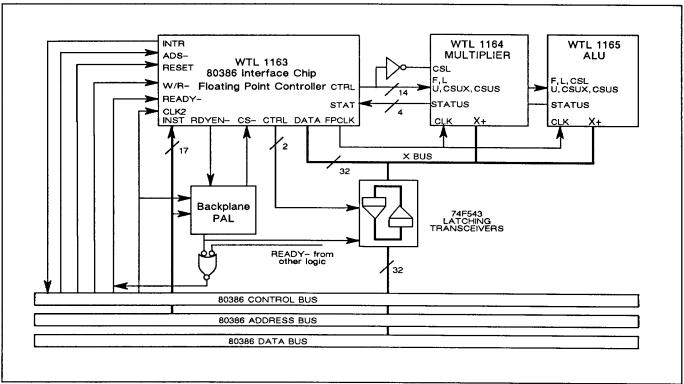

The simple interface and high speed of the WTL 1164/1165 make it an ideal chip set for accelerating the floating point performance of popular microprocessors. All of the control required to implement the interface between the microprocessor and the WTL 1164/1165 can be put onto one chip.

The WTL 1163 furnishes the interface between the WTL 1164/1165 and Intel's 80386. The three chip set can then provide 3.5 megaWhetstone performance. The chip set is fully supported with Fortran, Pascal and C compilers. A block diagram of the three chip set showing the system interface is shown below.

Figure 24. Coprocessor Block Diagram

For more information on coprocessor interface chips, call WEITEK.

# **IEEE Compatibility**

The IEEE Standard for Binary Floating Point specifies floating point processor data formats, rounding modes and exception handling. The WTL 1164 and WTL 1165 conform to the specification. The discussion

below reviews IEEE implementation on the WTL 1164/1165. A separate note describes how denormalized numbers (DNRMs) are handled.

#### DATA FORMATS

The WTL 1164/1165 perform both 32-bit and 64-bit IEEE standard floating point operations. The 32-bit

format has a 24-bit sign-magnitude fraction field and an 8-bit exponent, in the following format:

|       |       | 31 30 23 22                   | 0                   |

|-------|-------|-------------------------------|---------------------|

|       |       | s e                           | f                   |

|       |       | 1 8                           | 23                  |

| е     | f     | value                         | name                |

| 255   | not 0 | none                          | NaN (Not A Number)  |

| 255   | o     | (-1) s infinity               | Infinity            |

| 1 254 | any   | (-1) * 2 * (1.f)              | Normalized number   |

| 0     | not 0 | $(-1)^{s} * 2^{-126} * (0.f)$ | Denormalized number |

| 0     | 0     | (-1) <sup>s</sup> * 0         | Zero                |

Exponent values for normalized single precision numbers range from one to 254, with exponents of zero and 255 being reserved for special operands. To calculate the value of a number in this format, the exponent is decremented by 127 (the "exponent bias" is +127), and the fraction has a one inserted before the

binary point. (This is called the hidden bit.) The value of the number is then (-1) S  $\times$  2<sup>e-127</sup>  $\times$  (1.f).

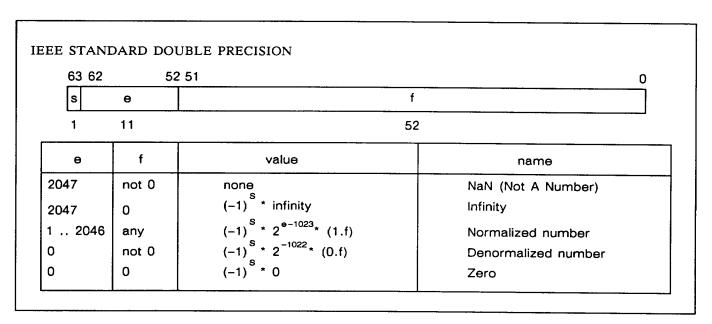

The 64-bit format has a 53-bit signed-magnitude fraction field and an 11-bit exponent, in the following format:

## IEEE Compatibility, continued

Exponent values for normalized double precision numbers range from one to 2,046 with exponents of zero and 2,047 being reserved for special operands. To calculate the value of a number in this format, the

exponent is decremented by 1,023 (the exponent bias is  $\pm 1,023$ ), and the fraction has a one inserted before the binary point. Thus the value of a double precision number is (-1)  $^{\rm S}$  X  $2^{\rm e-1023}$  X (1.f).

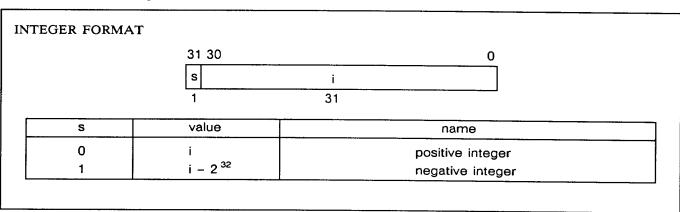

#### INTEGER FORMAT

The WTL 1164/1165 family supports conversion operations to and from 32-bit two's complement integers. The format is given below.

# WTL 1164/WTL 1165 64-BIT IEEE FLOATING POINT MULTIPLIER/ DIVIDER AND ALU

## PRELIMINARY DATA

## IEEE Compatibility, continued

Several number types are required to implement the standard. These are normalized numbers, denormalized numbers, wrapped numbers, infinity and zero.

#### Normalized Numbers (NRM)

Most caculations are performed on normalized numbers. For single precision, normalized numbers have an exponent that ranges from 00000001 to 11111110 (one to 254) and a normalized fraction field (the leftmost or hidden bit is a one). In decimal notation, this allows one to represent a range of both positive and negative numbers from roughly  $10^{38}$  to  $10^{-38}$  with accuracy to seven decimal places. Double precision numbers have an exponent ranging from one to 2,046 and a normalized fraction field.

#### Infinity (INF)

Infinity has an exponent of all ones and a fraction field equal to zero. Both positive and negative infinity are allowed.

#### **ZERO**

ZERO has an exponent of zero, a hidden bit equal to zero and a value of zero in the fraction field. Both +0 and -0 are supported.

#### Wrapped Numbers (WNRM)

A wrapped number is created by normalizing a DNRM's fraction field and subtracting from the exponent the

number of shift positions required. (Normalizing is accomplished by left shifting until the hidden bit contains a one.) The value of the exponent is equal to (1 – (the number of shifts)) and is represented in two's complement.

#### Unrounded Normalized Number (UNRM)

A UNRM is the result of an operation that has a magnitude less than the minimum representable normalized number. A UNRM has a normalized fraction field, a wrapped exponent and a hidden bit equal to one. The minimum UNRM is attained by multiplying two DNRM.MINs. UNRMs are turned into DNRM values using the ALU's unwrap function.

#### Denormalized Numbers (DNRM)

Denormalized numbers have a zero exponent and a denormalized (hidden bit equal to zero) non-zero fraction field.

#### Not A Number (NaN)

NaN, or not a number, is a special data format usually used as a flag for data flow control, for uninitialized variables or to signify an invalid operations such as  $0 \times \infty$ . The format for a NaN is an exponent of all ones and a non-zero fraction.

#### IEEE SINGLE PRECISION FORMATS SUPPORTED BY THE WTL 1164/1165

| OPERAND         EXPONENT         FRACTION         HIDDEN BIT         VALUE           Nan         255         ANY         N/A         NONE           INFINITY         255         ALL 0's         1         (-1) s ∞           NORM.MAX         254         ALL 1's         1         (-1) s × 2 127 × (2)           NORM         1 to 254         ANY         1         (-1) s × 2 126 × (1.f)           NORM.MIN         1         ALL 0's         1         (-1) s × 2 126 × (1.f)           DNRM.MAX         0         ALL 1's         0         (-1) s × (2.126 × 2.126 × (1.f)           DNRM.MIN         0         ANY         0         (-1) s × 2.126 × (0.f)           DNRM.MIN         0         00001         0         (-1) s × 2.126 × 2.23           WNRM.MAX         0         ALL 1's         1         (-1) s × 2.126 × 2.23           WNRM.MIN         -22         ANY         1         (-1) s × 2.126 × 2.126           UNRM.MAX         0         ALL 1's         1         (-1) s × 2.126           UNRM.MIN         -22         ALL 0's         1         (-1) s × 2.126           UNRM.MIN         -171         ALL 0's         1         (-1) s × 2.126           UNRM |          |            |          |            |                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|----------|------------|------------------------------------------|

| INFINITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OPERAND  | EXPONENT   | FRACTION | HIDDEN BIT | VALUE                                    |

| NORM.MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NaN      | 255        | ANY      | N/A        |                                          |

| NORM         1 to 254         ANY         1         (-1) s × 2 - 126 × (1.f)           NORM.MIN         1         ALL 0's         1         (-1) s × 2 - 126 × (1)           DNRM.MAX         0         ALL 1's         0         (-1) s × 2 - 126 × (2 - 2 - 2)           DNRM.MIN         0         ANY         0         (-1) s × 2 - 126 × (0.f)           DNRM.MAX         0         ALL 1's         1         (-1) s × 2 - 126 × (2 - 23)           WNRM.MAX         0         ALL 1's         1         (-1) s × 2 - 126 × (2 - 23)           WNRM.MIN         -22         ANY         1         (-1) s × 2 - 126           WNRM.MIN         -22         ALL 0's         1         (-1) s × 2 - 126           UNRM.MAX         0         ALL 1's         1         (-1) s × 2 - 126           UNRM.MIN         -171         ALL 0's         1         (-1) s × 2 - 298                                                                                                                                                                                                                                                                                                                   | INFINITY | 255        | ALL 0's  | 1          | (-1) ⋅ ∞                                 |

| NORM         1 to 254         ANY         1         (-1) s X 2 - 126 X (1.f)           NORM.MIN         1         ALL 0's         1         (-1) s X 2 - 126 X (1)           DNRM.MAX         0         ALL 1's         0         (-1) s X 2 - 126 X (1.f)           DNRM.MIN         0         ANY         0         (-1) s X 2 - 126 X (0.f)           DNRM.MAX         0         ALL 1's         1         (-1) s X 2 - 126 X 2 - 23           WNRM.MAX         0         ALL 1's         1         (-1) s X 2 - 126           WNRM.MIN         -22         ANY         1         (-1) s X 2 - 126           WNRM.MAX         0         ALL 1's         1         (-1) s X 2 - 126           UNRM.MAX         0         ALL 1's         1         (-1) s X 2 - 126           UNRM.MIN         -171         ALL 0's         1         (-1) s X 2 - 298                                                                                                                                                                                                                                                                                                                                        | NORM.MAX | 254        | ALL 1's  | 1          | $(-1)^{8} \times 2^{127} \times (2)$     |

| NORM.MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | NORM     | 1 to 254   | ANY      | 1          | $(-1)^{-1} \times 2 \times (1.t)$        |