Development Hardware

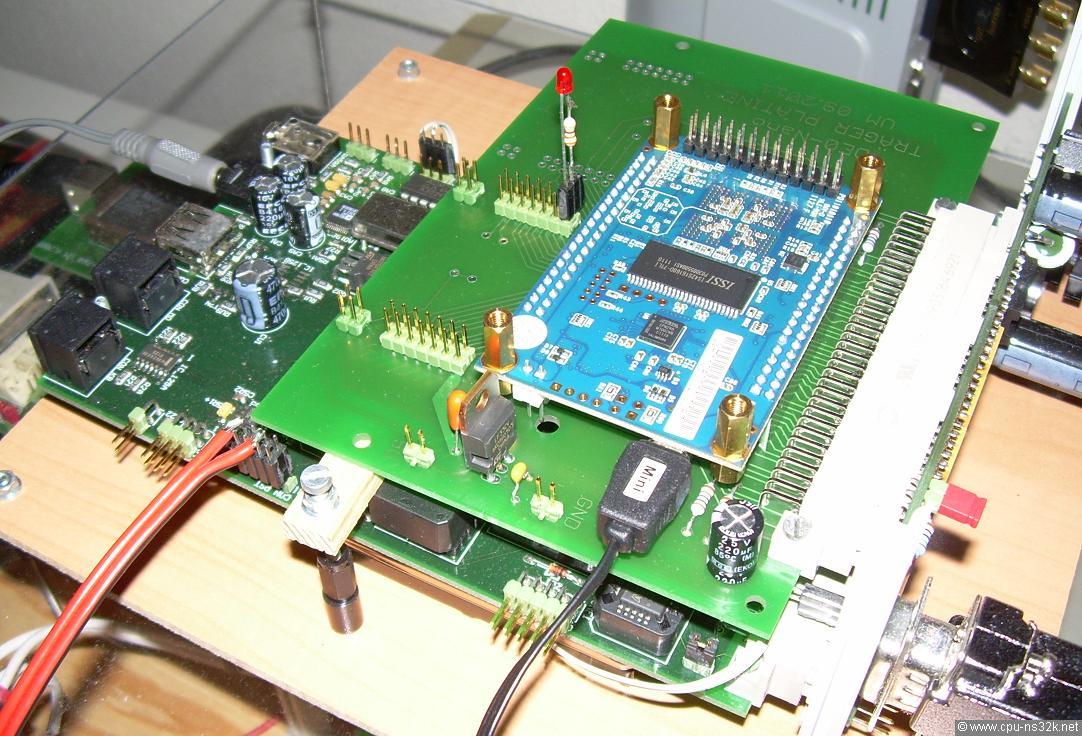

The design of the M32632 started on a self-developed board. The FPGA used is a member of the Cyclone II family from Altera. The EP2C20Q240-8 contains 18752 logic elements and is used together with 64 Mbytes of DDR DRAM. The first application of this board was as a graphic interface for my TITAN3 system. Below the Cyclone II board an I/O board of the TITAN3 is placed. A 2.5 inch HDD is placed below the I/O board. All together is mounted on a wooden carrier (building cases is not my strength). Figure 1 shows the complete system.

Fig. 1. The first developement system for the M32632.

The Cyclone II system is compatibel to my TITAN3 system. This allows it to run my own software without modifications. And you need complex software to debug a microprocessor like the M32632. If there is a bug and you are not able to modify the software to catch the bug you are in a bad position. Modifying software means you have all the source code and knows exactly what is happening inside the software. This maybe a problem later when I want to run the NetBSD code as a final test for the M32632 and the system crashes ...

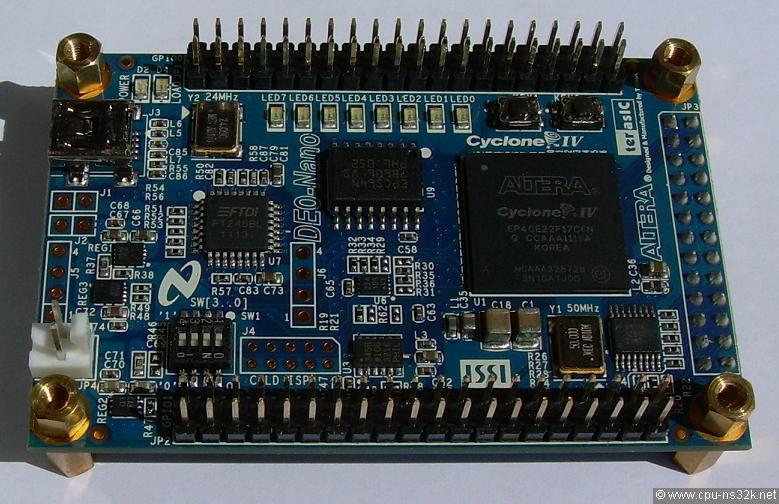

In 2011 I got problems with the Cyclone II and the Quartus Software. When the design filled 75% of the capacity of the Cylcone II device simulation results were wrong. I could not find a solution for this problem. But luckily a new board from Terasic offered a cheap solution : the DE0-Nano. This board is based on the Cyclone IV-E device EP4CE22F17C6N which has 22320 logic elements, slightly more then the Cyclone II device. Surprisingly the Cyclone IV family is remarkably faster then the Cyclone II family. The DE0-Nano board has a 32 Mbytes SDRAM and in addition some peripherals which are not used in my system. I build a simple carrier board for the DE0-Nano and replaced the Cyclone II board in my development system.

Fig. 2. The DE0-Nano board from Terasic.

Fig. 3. The upgraded development system for the M32632. The DE0-Nano board is mounted face-down.

Next chapter: PC632M