Ceres

The Ceres family of computers was build at the ETH Zürich by a team of Professor N. Wirth. The computers were advanced designs with a high resolution black-and-white display and a mouse interface. The system software was designed by N. Wirth and here name was Oberon.

I visited the ETH Zürich in May 2012. I met Professor J. Gutknecht, a former assistent and colleague of Professor N. Wirth, and some of his colleagues. They gave me the opportunity to take photos and to collect information.

Fig. 1. In the basement of the ETH Zürich : where is the Ceres ?

Ceres (1)

The first Ceres machine was based on the NS32032 CPU. Not surprisingly no machine has survived more than 25 years. Also no photos were available. This was my state of knwoledge until May 2017.

In this month I found by chance in Ed's post to the Retro Computing community a hint to a Ceres at the Computer History Museum in Mountain View, California/USA. Their website presents the machine and the pcbs together with some text. The pcbs are similar to the ones of the Ceres-2. Hopefully the store of the Computer History Museum is a robust building...

Two documents describe the implementation in detail. The first is called "Hardware Description of the Workstation Ceres" and the second is the dissertation ETH No. 8431 named "Development and Analysis of a Workstation computer".

Ceres : Hardware Description (PDF)

Ceres : Dissertation ETH No. 8431 (PDF)

Ceres-2

The next generation Ceres machine was based on the NS32532 CPU. A document named "Design of the Processor-Board for the Ceres-2 Workstation" gives a good overview.

Ceres-2 : Design of the Processor-Board (PDF)

Fig. 2. The robust case of the Ceres-2.

Fig. 3. Inside view of the Ceres-2.

Fig. 4. The CPU board of the Ceres-2.

The CPU board of the Ceres-2 is not so densly populated with chips like other designs. This would allow to use a PCB with less layers which is cheaper.

Fig. 5. The memory boards of the Ceres-2.

The Ceres-2 has two memory boards. On the left side is the main memory build from Siemens HYB511000. The populated capacity is 4 Mbytes with parity and spare sockets for additional 4 Mbytes. On the right side is the video memory build from Texas Instruments DRAMs. Capacity is 256 kbytes according to the memory map with no parity. A higher resolution photo of the memory boards is available :

Ceres-2 memory boards in high resolution (JPEG)

Ceres-3

The last Ceres generation, Ceres-3, used the NS32GX32 CPU. This CPU is compatible to the NS32532 CPU but does not contain the MMU. Therefore the NS32GX32 is cheaper than the NS32532. For Ceres-3 and Oberon a full blown MMU function is not neccesary. A document named "Hardware Description of the Workstation Ceres-3" can be downloaded here :

Ceres-3 : Hardware Description (PDF)

An interesting design detail of the Ceres-3 is the power supply of the computer (see Figure 11). There is only one cable between the monitor and the Ceres-3 : video signals are sent from the computer to the monitor and power is delivered from the monitor to the computer. Therefore you can not see any bulky power components inside the Ceres-3.

Fig. 6. The remarkable beautiful case of the Ceres-3.

Fig. 7. Inside view of the Ceres-3.

Fig. 8. The CPU part of the mainboard of the Ceres-3.

Fig. 9. The memory part of the mainboard of the Ceres-3.

Main memory of the Ceres-3 was 8 Mbytes DRAM build of memory modules. Each module had 1 Mbytes with the parity chip position left open. Behind the memory modules you can see on the above photo 8 devices which are packaged in a vertical 24 pin SIP. These chips are so called Video-RAMs (VRAM) . A VRAM is a normal DRAM for the CPU but it has an additional shift register build in. The shift register was mostly 256 bits in length and could be loaded in parallel from the memory array. The main purpose was to minimize the overhead for screen refresh. But VRAMs were more expensive than ordinary DRAMs and therefore this concept is no longer in use.

The video in the link shows at the end Professor N. Wirth working on a Ceres-3 during a presentation in May 2011.

At least one other Ceres-3 workstation survived and is still functional. Paul Reed promised me to power-up the system from time to time to check if it is still ok. The Ceres-3 is a good candidate for a nice project based on the M32632 CPU.

Ceres-3 in Action

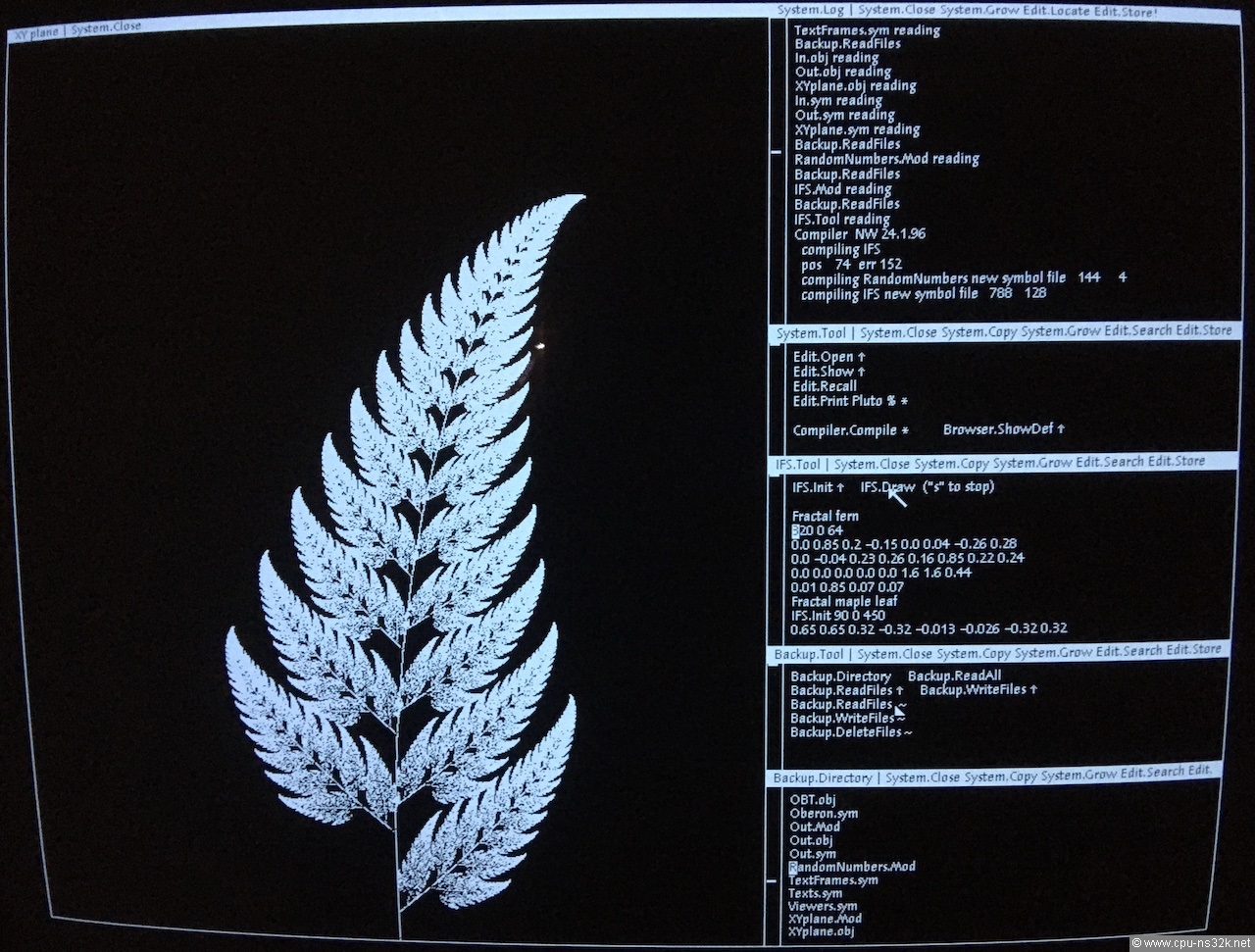

In June 2023 Paul Reed switched on his Ceres-3. Everything worked fine. The next Figure is the proof.

Fig. 10. This photo shows the impressive quality of the black-and-white CRT monitor.

Fig. 11. The backside of the system shows the modified monitor which contains the power supply for the computer.

Miscellanous

Professor N. Wirth designed a network for the Ceres machines. The goals and the technology used are described in a document which can be downloaded here :

This chapter was last modified on 12 August 2023. Next chapter: CompuPro