Tolerant Systems

In July 2024 I received an email telling me something about a company named Tolerant Systems. I have never heard about this company until I got the email. The author gave more details:

"I worked at Tolerant Systems who embraced the 32K architecture whole-heartedly. I have a communications processor board that I designed for Tolerant using a 32016 CPU and and 4 of the 32203 DMA chips. This allowed 16 channels of DMA - most of which were used by the 12 Zilog SCC channels (6 chips). We also had a hardware driven DMA channel for the Centronics interface. You could program a buffer for any of the channels and the DMA would move it out over the respective channel without any further CPU intervention.

The board ran a Real Time Executive that was a Tolerant Systems proprietary RTE. Note - Tolerant later got out of the Hardware business an changed their name to Veritas (which became a multi-billion dollar software firm...)

I still have a version of this board in my possession with the 16032 and the 4 DMA controllers!"

If you want to know more about the history of Tolerant Systems and Veritas please have a look at Wikipedia.

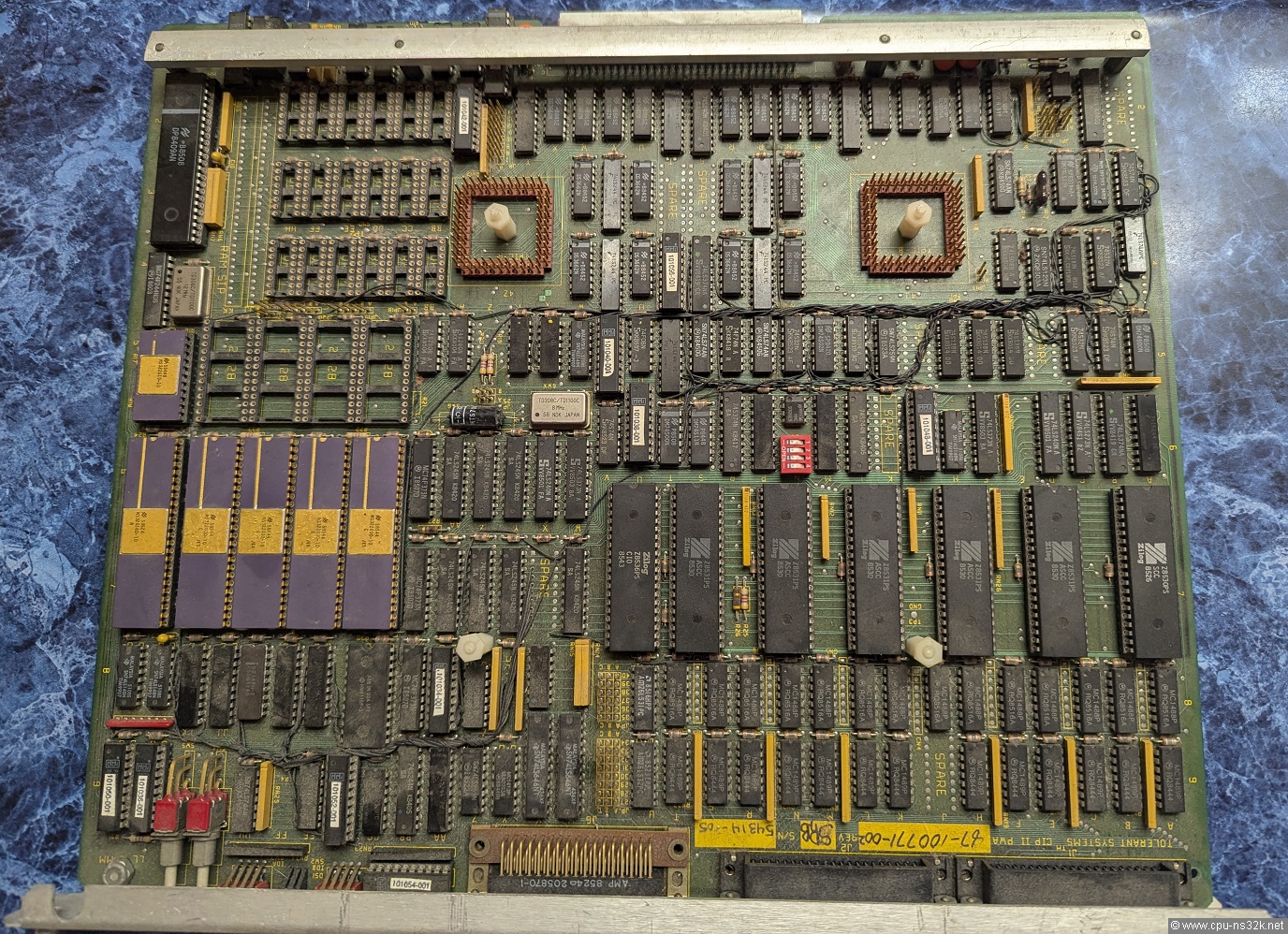

The last sentence in his email contains the kind of message which makes me extremly curious - unknown Series 32000 hardware in sight! Of course I asked for a photo and here it is:

Fig. 1. Wow - the Communication Interface Processor is a huge piece of hardware. If you want to see more details please look here.

The owner wrote another email telling more about the board and the system:

"The 5 devices in the lower left are a NS16032 + 4 NSC DMA controller. There are 12 serial channels implemented by Zilog SCC chips ( same as used in the MAC). The board also supports a Centronics printer port and two Tolerant IO channels (implemented in two daughter cards that mounted above the board...this later was implemented in a custom ASIC)

We had a thing we called a system building block SBB...which was a computing node. It contained a system processor, job processor and IO processor. The system and Job processors were 32032 systems. The IOP was a 16032 based system. We had a dual enet on the system processor and you could string multiple SBBs together. It ran a version of 4.2 BSD called TX. When you logged into TX you had a single file system view even though the file system could be spread across multiple Disks and SBBs. It also had one of the earliest journaling file systems that was bullet proof from power failures. This is what was later developed into the Software products of Veritas.

The IO system was also doubled up. There were 2 Io channels that each peripheral would talk too that would be different SBBs. The IO channel ran a 3 M byte/sec and was best for block data transfer. They had their own disc controller, tape drive and com processor.

The Communication Interface Processor that I designed had a special feature that would collect serial data up until a carriage return was hit. It would do local echo of characters typed in by the user ( a unix behavior). This had two advantages. First it unloaded the high interrupt rate to the job processors on the SBBs. It also made more efficient use of a block mode IO channel!"

I noticed one lonely Intel D2147 SRAM on the board, just below the second NS32203 DMA controller. It is organized as 4096 by 1 bit. I asked him about its use and his answer shows an advanced level of design skill:

"The sram was used as a table look up for bisync protocol. The characters being transmitted by Dma when running bisync would be used as a table lookup to decide to assert a signal to stop the DMA and interrupt the CPU. Bisync has a data and control characters embedded in it. This was how the system could use DMA and still support the protocol when CPU intervention was required."

The design of Tolerant Systems is very impressive. It would be great if photos of the other boards could be presented.

This chapter was created on 6 July 2024. Next chapter: Trinity College